# Design and Simulation of Phased Arrays For Radar/Aerospace Applications

By Gent Paparisto, Ph.D., AWR Group, NI

Phased array antenna systems, which use sets of two or more antennas, offer improved performance over single antennas and are well-known for their usefulness in radar and aerospace applications. Phased arrays are seeing increased use in automotive, satellite, public safety, and advanced wireless communications systems. Communication system design software, such as NI AWR Design Environment/Visual System Simulator (VSS), supports the design and analysis of phased arrays, as well as their implementation in a system of antenna elements, power divider/combiners, phase shifters, and other typical components. This article examines how software can be used to simulate both small and large phased arrays in typical configurations.

#### **Defining The Task**

Design software for complex communication systems enables engineers to examine system architectures, and to formulate suitable specifications for each of the underlying components. In the case of a phased array, the designer will use antenna and component characterizations obtained from various design tools or from measurements, and then place them into the desired array configuration. The entire system then can be simulated, studied, and optimized to achieve design goals.

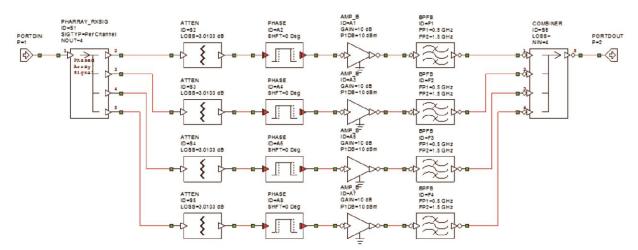

Tools can be used to simulate phased arrays with hundreds of elements. In VSS, for example, configuration of the array hardware can be done interactively using the GUI, entered as equations, or imported as a data file. Beamforming algorithms involving current taper, phase shift, and geometry may be implemented similarly. A typical implementation will use discrete blocks (Fig. 1), including power dividers, attenuators, phase shifters, and amplifiers. Each block contributes to the final definition of gain and relative phase for each antenna element. The entire system then can be analyzed for optimum performance, evaluated for the effects of hardware impairments, and evaluated in a complete end-to-end system.

Fig. 1: Phased arrays typically are implemented using discrete blocks.

# **Phased Array Configurations**

The antenna designer has a wide range of options, as shown in Fig. 2, the main setup screen. Array definitions include:

- TX/RX modes and signal distribution method (e.g., power divider)

- Distance units (metric, imperial, or in wavelength, λ)

- Signal frequency (when units are not  $\lambda$ )

- Steering angles

- Angles of incidence

- Gain taper settings

- Array imperfections (if desired)

Fig. 2: Setup screen in design tool phased array.

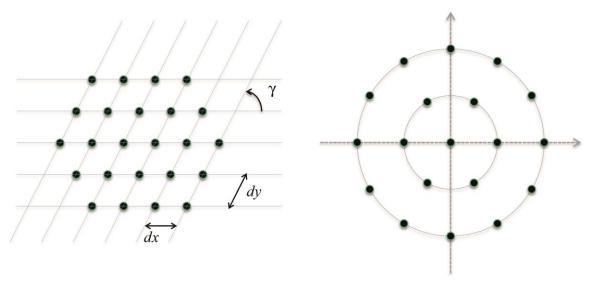

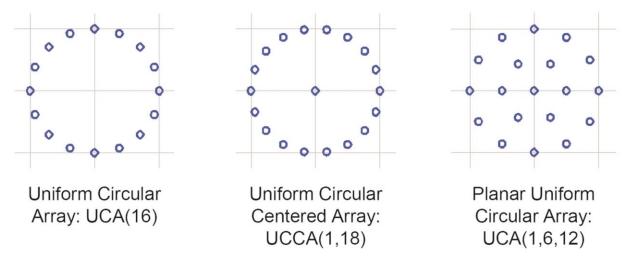

Standard architectures include rectangular and triangular lattice structure, or a circular geometry with elements in multiple concentric circles (Fig. 3). Custom architectures may be defined by *x-y* locations, pseudo-random distribution, or as multiple panels of element groups.

Fig. 3: Standard array geometries include rectangular or triangular lattice and concentric circle configurations.

The choice of gain taper affects sidelobe performance. Standard tapers include a uniform taper: Dolph-Chebyshev for low sidelobe ratio, and Taylor for near-equal sidelobes. User-defined tapers can be used to define gain and phase for each element.

To analyze the performance of the array with imperfections, the user may choose geometry errors (offset from defined *x-y* locations), gain and phase errors, and failed elements as either a percentage of elements at random or a selection of specific array elements.

RF links for each element can be provided as a configuration file that includes either measured data, or the results of design and simulation using external design tools. Typical or individual performance characteristics may be defined for the array elements. Some tools can individually characterize the RF link for each element, where an analysis is run once and the results are stored in a file, as is done with data from external tools.

Finally, the array is characterized for antenna pattern, array response, half-power bandwidth (HPBW), and other typical parameters. This is done in the phased array test bench, which supports RF analysis and planning, including system level simulations with modulated signals.

# **Examples**

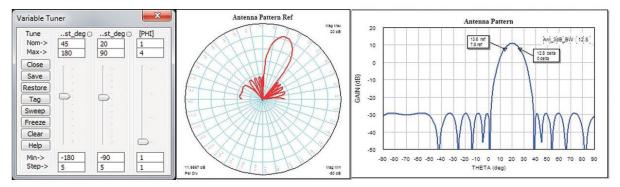

Linear Array — Fig. 4 shows the rectangular and polar pattern plots for a linear array with 16 elements and  $\lambda/2$  spacing,  $N_x = 16$ ,  $d_x = \lambda/2$ . The array uses a Dolph-Chebyshev taper to achieve 40 dB sidelobe ratio, and has steering angles defined as:  $\theta = 15^{\circ}$  and  $\phi = 45^{\circ}$ , where  $\theta$  is the *x* axis, in line with the elements' linear arrangement. The HPBW of the array is 12.8°.

Fig. 4 (L to R): Linear array example: tuner, polar, and rectangular pattern plots.

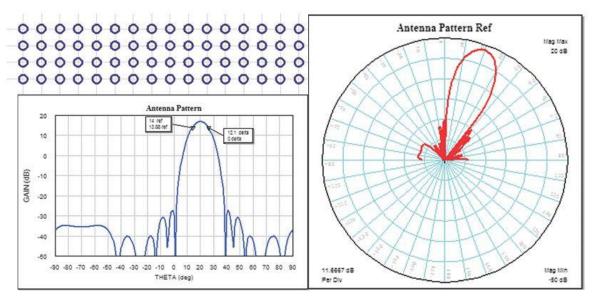

Planar Array — This example is a rectangular  $4 \times 16$  element lattice with 1/2 spacing,  $N_x = 16$ ,  $N_y = 4$ ,  $d_x = d_y = \lambda 1/2$ . This array also uses a Dolph-Chebyshev taper for 40 dB sidelobe ratio in the x direction. The layout of the elements and results of the simulation are illustrated in Fig. 5, showing a HPBW of 12.1°.

Fig. 5: Planar array example (Clockwise, from top left): Element configuration, polar, and rectangular plots.

Circular Array — Fig. 6 illustrates three standard circular array configurations, defined in vector notation as: number of elements  $N_c$ , radius R, and angular increment  $f_0$ .

Fig. 6: Circular array configuration types.

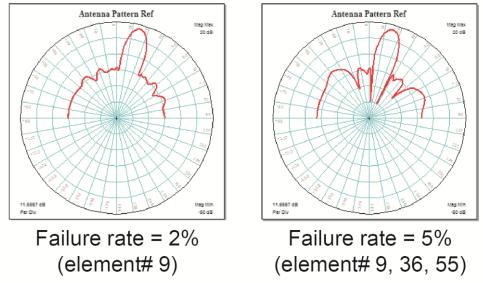

Analysis of a phased array begins with the antenna patterns and related explorations of current taper algorithms and beam steering. Modification and optimization may be applied to reach the design goals. Once the desired pattern behavior is obtained, the effect of impairments typically is examined to identify the loss of performance in the event of element failure and electronic failure or errors. Fig. 7 is an example of element failure analysis for the linear array example illustrated in Fig. 4. The plots with 2 percent and 5 percent failure rates clearly show the extent of pattern degradation, demonstrated by

increased sidelobe amplitude. Phase error analysis for the same array is shown in Fig. 8, where the applied 5° offsets between elements result in a shift in position of the main lobe, changing the sidelobes, as well.

Figure 7: Element failure analysis results.

*Figure 8: 5-degree phase error (signal distribution delay error) results.*

Once the antenna itself is characterized, total system performance may be analyzed to evaluate the array over a range of power levels and/or frequencies. Typical path analysis also may be done, including overall noise figure (NF),  $P_{1dB}$  determination, and link budget calculations such as path loss, signal-to-noise ratio (SNR), and complete end-to-end system simulation. All of these design, optimization and analysis steps are done quickly and efficiently, allowing the antenna designer to obtain the desired performance while keeping system development on schedule.

#### Summary

Communication systems design software now offers advanced capabilities for designing phased array antennas. These new features provide the capability for design and evaluation of very large arrays. Configuration is uncomplicated, so antenna designers spend less time in setup and more time designing. With these design and analysis tools, users can produce designs that match real-world results, including accounting for hardware imperfections.

#### **About The Author**

Dr. Gent Paparisto is a senior systems engineer at AWR Group, NI. He received his Ph.D. in electrical engineering from the University of Southern California (USC) and has extensive experience in research, design, development, and implementation of communication systems and algorithms for wireless, satellite, and wireline applications. Dr. Paparisto has authored a number of publications in international journals and

conferences, served on the technical program committees of various IEEE conferences, and contributed to the 3GPP GERAN standardization group.